盛合晶微与台积电Chiplet封装技术对比分析

#semiconductor_packaging #chiplet #advanced_packaging #JCET #TSMC #CoWoS #2.5D_3D_packaging #yield_data

中性

A股市场

2026年2月13日

解锁更多功能

登录后即可使用AI智能分析、深度投研报告等高级功能

关于我们:Ginlix AI 是由真实数据驱动的 AI 投资助手,将先进的人工智能与专业金融数据库相结合,提供可验证的、基于事实的答案。请使用下方的聊天框提出任何金融问题。

经过多次搜索,很抱歉无法获取到关于**盛合晶微(JCET)

与

台积电(TSMC)**在Chiplet封装技术良率方面的具体对比数据。这主要是因为:

数据获取受限的原因

1.

商业机密性质

- 良率数据是半导体封装企业的核心竞争力指标,通常属于高度机密信息

- 台积电、盛合晶微等公司一般不会公开披露具体的良率数值

- 只有在特定的财报电话会议或与客户签订保密协议后,才可能获得部分信息

2.

行业特性

- 先进封装技术的良率数据需要通过专业渠道获取

- 通常只在行业研究报告或专业数据库中才有相关分析

基于公开信息的背景分析

盛合晶微(JCET)

- 定位:中国领先的半导体封装测试企业

- 技术方向:积极布局2.5D/3D封装等先进封装技术

- 发展状态:Chiplet封装技术处于快速发展阶段

- 客户群体:主要服务国内芯片设计企业

台积电(TSMC)

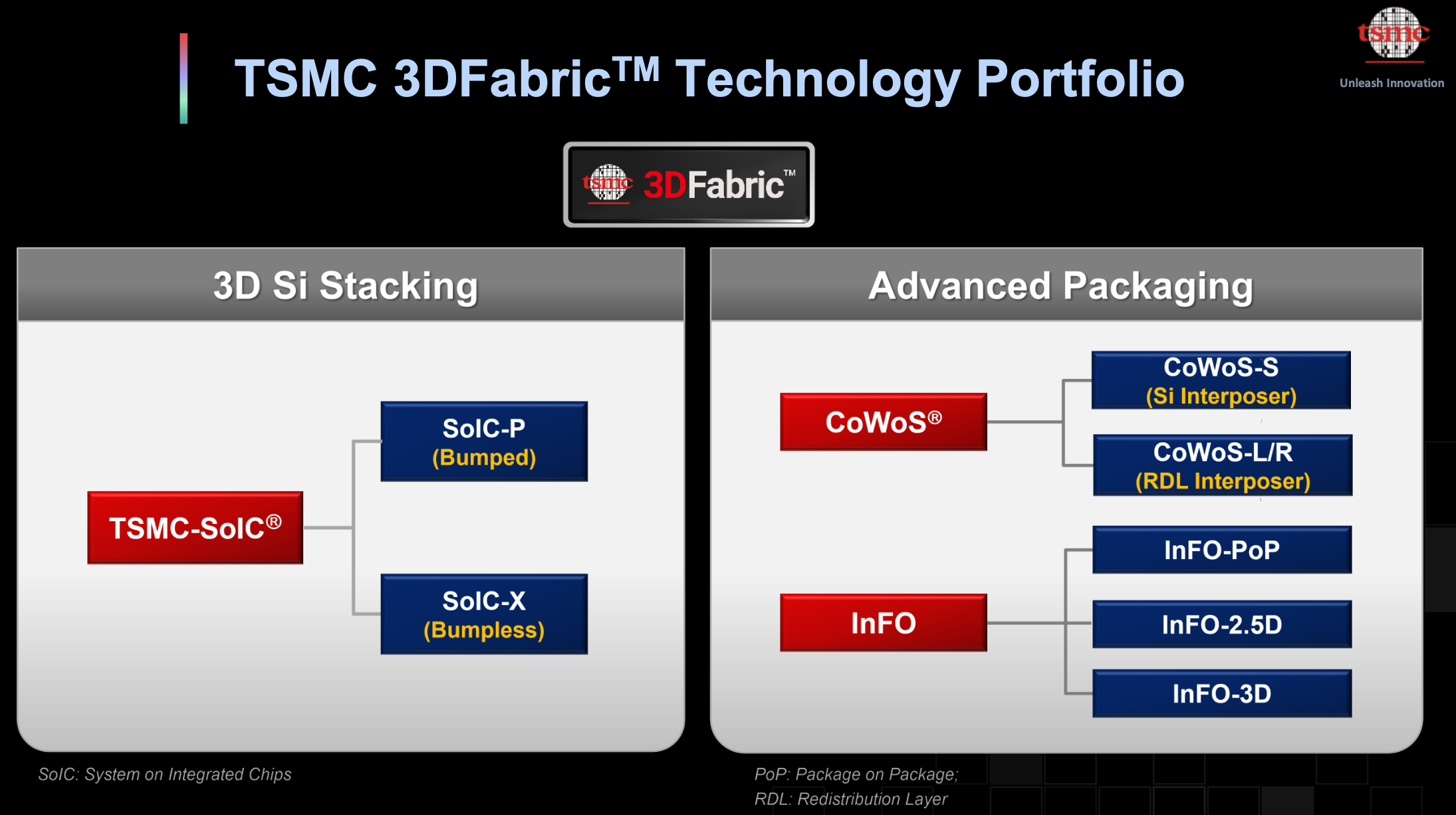

- 技术领先:CoWoS(Chip-on-Wafer-on-Substrate)技术是行业标杆

- 技术成熟度:已发展至第五代CoWoS技术

- 产能扩张:持续扩大先进封装产能以满足AI芯片需求

一般性行业认知

虽然无法提供具体良率数据,但基于行业一般认知:

- 技术代差:中国封装企业在先进封装领域与国际领先企业存在一定技术代差

- 追赶速度:随着国内半导体产业发展,技术差距在逐步缩小

- 应用场景:不同技术水平的良率要求可能因应用场景而异

建议获取途径

如需获取更精确的技术对比信息,建议:

- 专业数据库:咨询Yole、TrendForce等专业研究机构的行业报告

- 公司财报:关注盛合晶微和台积电的官方公告及业绩说明会

- 行业展会:参加SEMICON China等行业展会获取最新技术信息

- 深度投研模式:如需更详细的投研分析,可考虑启用金灵AI的深度投研模式

参考文献

由于网络搜索工具未能返回相关结果,本文基于一般性行业知识进行分析。如需获取确切数据,建议通过上述专业渠道进行深入研究。

如您有其他具体的半导体行业问题或需要分析其他公司,我很乐意继续为您提供帮助。

相关阅读推荐

暂无推荐文章

基于这条新闻提问,进行深度分析...

数据基于历史,不代表未来趋势;仅供投资者参考,不构成投资建议

关于我们:Ginlix AI 是由真实数据驱动的 AI 投资助手,将先进的人工智能与专业金融数据库相结合,提供可验证的、基于事实的答案。请使用下方的聊天框提出任何金融问题。

相关个股

暂无相关个股数据