盛合晶微12英寸凸块量产技术壁垒分析

#半导体 #先进封装 #凸块制造 #技术壁垒 #科创板 #12英寸晶圆 #国产替代

积极

A股市场

2026年2月14日

解锁更多功能

登录后即可使用AI智能分析、深度投研报告等高级功能

关于我们:Ginlix AI 是由真实数据驱动的 AI 投资助手,将先进的人工智能与专业金融数据库相结合,提供可验证的、基于事实的答案。请使用下方的聊天框提出任何金融问题。

根据搜索到的信息,我来为您详细分析盛合晶微12英寸凸块量产的技术壁垒。

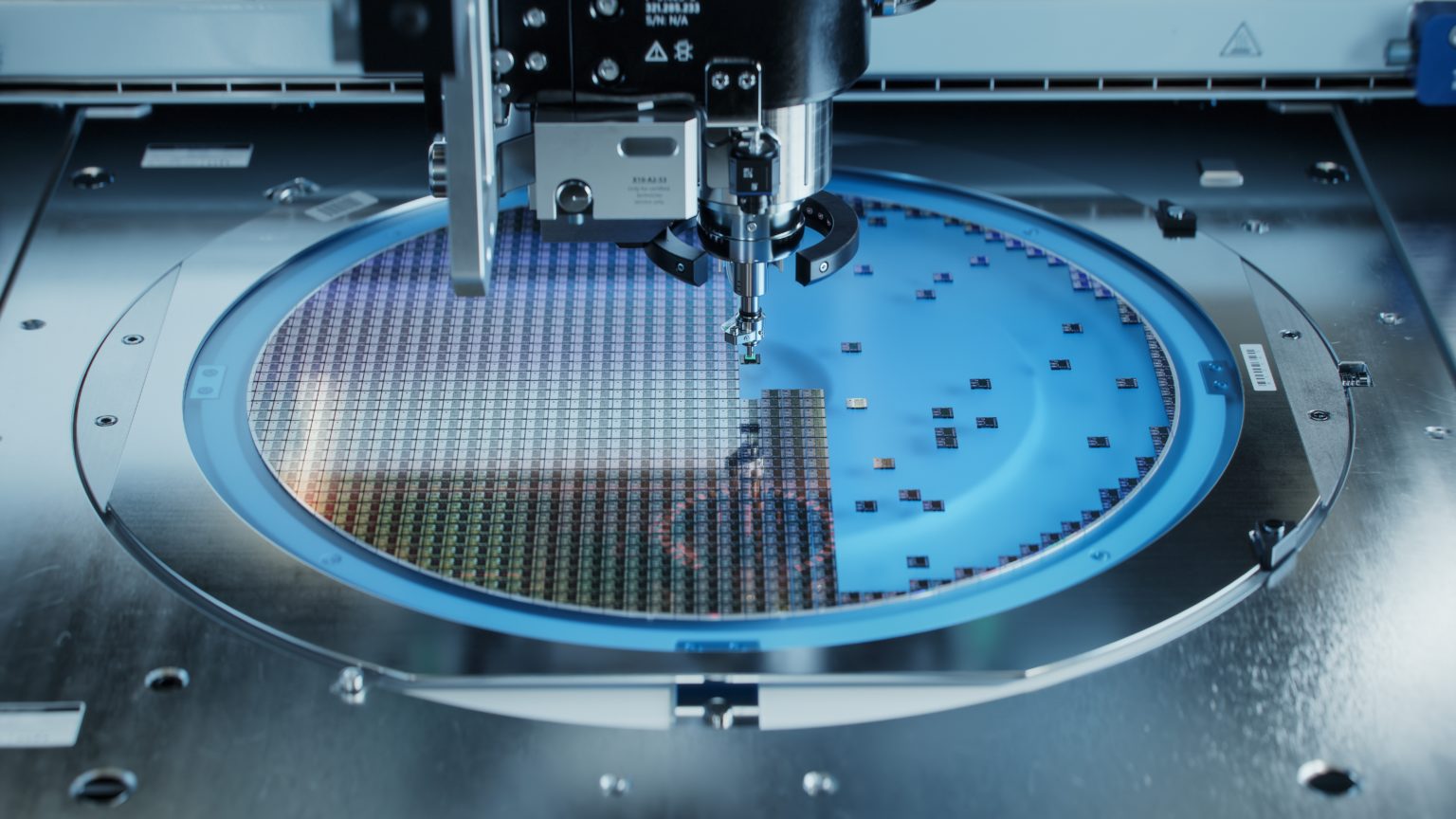

盛合晶微12英寸凸块量产技术壁垒分析

一、技术壁垒的核心难点

1. 制程精度要求极高

- 盛合晶微可量产实现20μm/12μm的凸块间距/直径,单颗芯片凸块数量可达数十万个[1]

- 凸块间距和直径的微缩对设备精度、工艺控制提出了极高要求

- 随着制程节点从28nm向14nm、7nm演进,凸块尺寸需要进一步微缩,技术难度呈指数级上升

2. 电镀工艺复杂

- 先进封装电镀工艺是形成互连结构(铜柱、凸块、RDL再布线层)的关键步骤[2]

- 添加剂浓度控制是核心技术难点:电镀液中的抑制剂、光亮剂等微量成分直接影响金属沉积的均匀性

- 浓度失衡可能导致孔洞、裂纹,甚至芯片失效

- 缺陷风险高,需要精密的质量控制体系

3. 14nm先进制程瓶颈

- 盛合晶微是中国大陆第一家能够提供14nm先进制程Bumping服务的企业[3]

- 14nm及以上制程的凸块制造需要克服:

- 更薄的晶圆加工

- 更高的I/O密度

- 更严格的表面平整度要求

- 更高的电气性能稳定性

二、盛合晶微的技术优势

| 指标 | 盛合晶微水平 | 国际龙头对比 |

|---|---|---|

| 凸块间距 | 20μm | 与日月光、安靠科技同一水平[1] |

| 凸块直径 | 12μm | 与日月光、安靠科技同一水平[1] |

| 制程能力 | 14nm | 中国大陆第一 |

| 12英寸Bumping产能 | 中国大陆首位 | - |

| 12英寸WLCSP市场份额 | 31%(2024年) | 中国大陆第一 |

三、技术壁垒的其他维度

1. 设备壁垒

- 12英寸晶圆加工设备精度要求远高于8英寸

- 凸块制造需要光刻、刻蚀、电镀、清洗等多项高精度设备

- 关键设备依赖进口,供应链受限

2. 量产经验积累

- 盛合晶微2017年启动12英寸大尺寸WLCSP服务开发,2018年实现量产[4]

- 长达8年以上的量产经验积累,形成 Know-how 护城河

- 良率控制和产能爬坡需要长时间工艺优化

3. 完整工艺流程整合

- 盛合晶微构建了从中段硅片加工到晶圆级封装、再到2.5D/3D多芯片集成封装的全流程能力[3]

- 这种垂直整合能力中国大陆极少有竞争对手具备

四、竞争格局与技术代差

盛合晶微在2.5D封装领域的技术指标(最小微凸块间距、最大硅转接板尺寸)

对标台积电、三星电子等全球晶圆制造巨头

[5]。

但在

3D混合键合技术

方面,公司承认与国际巨头仍存在一定的差距

[5],这代表了未来技术发展方向的主要挑战。

结论

盛合晶微12英寸凸块量产的技术壁垒主要体现在:

- 制程精度壁垒:20μm/12um的凸块间距/直径达到国际先进水平

- 工艺控制壁垒:电镀工艺的添加剂浓度控制、缺陷检测难度极高

- 先进制程壁垒:14nm Bumping技术中国大陆唯一

- 量产经验壁垒:8年以上量产经验积累

- 设备壁垒:12英寸高精度设备依赖进口

盛合晶微成功突破了这些技术壁垒,成为中国大陆12英寸凸块制造的领导者,技术指标已与日月光、安靠科技等国际龙头处于同一水平[1]。

参考文献

相关阅读推荐

暂无推荐文章

基于这条新闻提问,进行深度分析...

数据基于历史,不代表未来趋势;仅供投资者参考,不构成投资建议

关于我们:Ginlix AI 是由真实数据驱动的 AI 投资助手,将先进的人工智能与专业金融数据库相结合,提供可验证的、基于事实的答案。请使用下方的聊天框提出任何金融问题。

相关个股

暂无相关个股数据